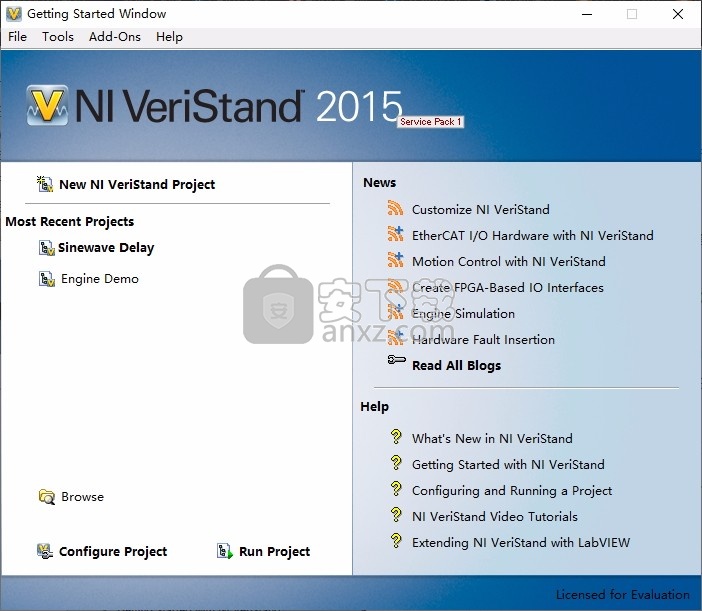

NI VeriStand 2015

附带安装教程- 软件大小:1239 MB

- 更新日期:2020-03-27 14:57

- 软件语言:简体中文

- 软件类别:辅助设计

- 软件授权:免费版

- 软件官网:待审核

- 适用平台:WinXP, Win7, Win8, Win10, WinAll

- 软件厂商:

软件介绍 人气软件 下载地址

NI VeriStand 2015是一款针对数据采集以及环境测试而开发的应用工具,内置了全新的测试模块,用户可以使用此工具在极短的时间之内实现检测硬件配置I/O通道以及数据记录;可为用户提供一个使用硬件I/O和仿真模型开发系统,同时支持原型设计和测试控制,该软件框架使用户能够执行实时或基于PC的测试配置和执行,可以使用LabVIEW,NI TestStand和其他软件工具轻松地对其进行自定义和扩展;新版本包括一个运行时可编辑的用户界面以及一个测试管理器,用户可以使用它来配置和实现触发的多文件数据记录,实时测试排序,激励生成和回放以及模型校准;新版本采用了最新的UI管理器,与工作区类似,UI管理器允许用户创建运行时可编辑的用户界面,也称为屏幕,操作员可以使用这些界面与程序项目进行交互;此模块还对工作区进行了一些改进,它提供了用于自定义对象外观和功能的多种选项,对具有多个屏幕的项目的多监视器支持;需要的用户可以下载体验

新版功能

1、VeriStand UI Manager—迅速开发专业的用户界面

UI Manager(用户界面管理器)使VeriStand呈现出全新的面貌。 经过彻底的重新设计,UI Manager将可优化您与VeriStand的交互方式。 现在,您可以快速、轻松地将UI元素部署到多个屏幕上,然后在运行测试时缩放和搜索所需的数据。

经改良的全新工具,提高实时测试效率

除了美化的外观之外,UI Manager还提供了一系列工具来提高测试效率。 现在,您可以在同一个屏幕上执行实时序列、调整模型参数、管理警报、记录数据和进行后期处理。

2、业界标准的自动化,最大化测试组件复用率—ASAM XIL API支持提高了VeriStand的灵活性

VeriStand 2015 SP1可本地支持业界标准的ASAM XIL API。 这可帮助您将NI硬件在环(HIL)系统与第三方HIL系统相集成,从而继续利用使用其他HIL环境开发的测试脚本。 现在您可随意选择所需的工具,无需担心会中断现有的工作流程。

3、在NI Linux Real-Time上运行VeriStand—支持ARM和Intel Atom CompactRIO设备

在搭载NI Linux Real-Time操作系统的CompactRIO控制器上配置和运行实时测试。 同时将小巧、坚固的组成结构与调理I/O结合,获得最新移动处理器和FPGA的强大实时性能。

4、VeriStand开发者社区

下载VeriStand附加工具,比如自定义工作区对象、实时引擎特性、测试序列和模型等。 您还可到VeriStand社区上提交您自己开发的附加工具程序。

软件特色

可以访问工具,而无需在UI Manager窗口之外生成其他对话框。 UI Manager中可用的一些工具包括:

“模型参数管理器”选项卡-在运行时配置模型参数的值。

您可以使用此工具来手动更新模型参数值或从文件导入批次的模型参数。

“警报监视器”选项卡-查看系统定义文件中所有警报的状态,在运行时配置警报的设置,以及启用和禁用警报。

通道故障管理器选项卡-将通道强制为特定值以测试系统的行为。

通道数据查看器选项卡-在运行时监视通道值。

错误和警告选项卡-跟踪错误,警告和消息。

日志记录规范文件-在运行时配置和执行主机端数据日志记录操作。

项目窗格-指定屏幕上任何控件或指示器的名称,通道分配和视觉属性。

文档窗格-指定屏幕的名称和视觉属性,包括背景。

系统定义面板-查看系统定义,以便您可以轻松地将通道映射到控件和指示器。

缩放控制-通过百分比或使用“适合屏幕”和“适合选择”选项来放大和缩小屏幕。

撤消和重做选项-撤消之前的操作并在您撤消它们后重复操作。

对齐,分配和排序按钮-快速排列所选项目。

绘图控件-使用图像和形状来自定义屏幕的外观。

警报LED指示灯-配置特定警报触发时闪烁的LED指示灯。

铃声控制-创建选项列表,操作员可以循环选择这些选项。

实时序列控制-在UI Manager中配置,运行,暂停和停止实时序列。您还可以查看序列的状态,时间和返回值。

文本和图像操作按钮-创建自定义文本或图像按钮以启动特定文件,例如.exe或.bat文件或网页。

标签和画布控件-将相关项目组与屏幕上的其他项目分开。选项卡控件可用于调出与操作的特定阶段相关的不同项目组。画布控件可用于调出相关项目组,同时仍在主屏幕上保持可见状态。

相对时间通道

NI VeriStand 2015 SP1包含两个新的日志时间通道,您可以将它们添加到TDMS文件通道组:

相对于首次启动触发器-指示从数据记录开始到由于启动触发器而开始的相对时间。

相对于会话开始-指示自数据记录会话开始以来的相对时间。

TopNI VeriStand ASAM XIL接口

自动化和测量系统标准化协会(ASAM)是一个组织,旨在促进不同供应商的测量和自动化测试工具之间的互操作性。为符合ASAM标准,NI VeriStand 2015 SP1包括一个基于ASAM XIL API版本2.0.1的模型访问端口(MAPort)的通用仿真器接口。您可以使用MAPort在模拟模型中读取和写入数据以及捕获和生成信号。

TopEmbedded UI支持

NI VeriStand 2015 SP1在带有显示端口输出的CompactRIO上支持NI MAX嵌入式UI选项。您可以在运行时查看自定义设备的前面板,这对于调试或为操作员提供自定义显示很有用。

TopCyclic /事件框架

循环/事件帧结合了循环和事件帧的功能,既可以周期性地传输,也可以在发生特定事件时进行传输。

安装步骤

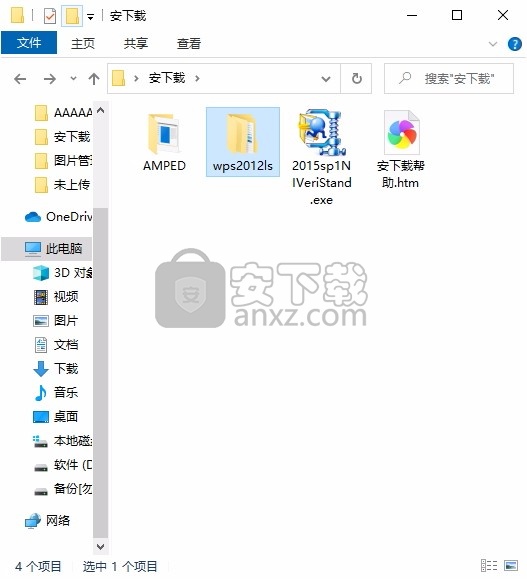

1、用户可以点击本网站提供的下载路径下载得到对应的程序安装包

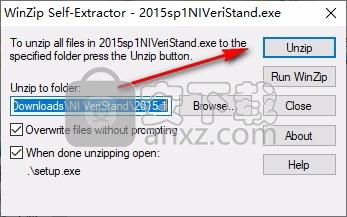

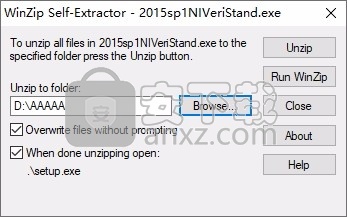

2、只需要使用解压功能将压缩包打开,双击主程序即可进行安装,弹出程序安装界面,点击unzip解压,可以更改路径

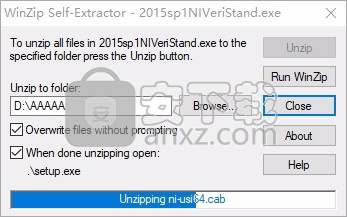

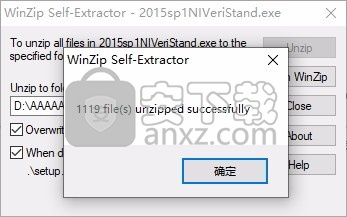

3、只需要等待一会儿就可以将程序数据包解压到指定的文件夹中,然后开始安装

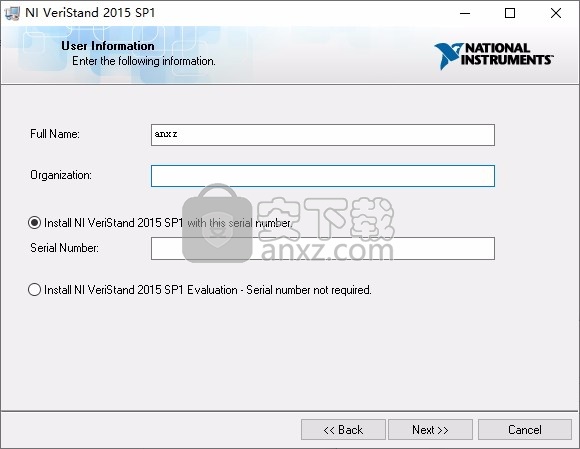

4、弹出一个提示窗口,用户可以随便输入名字,也可以参考小编的

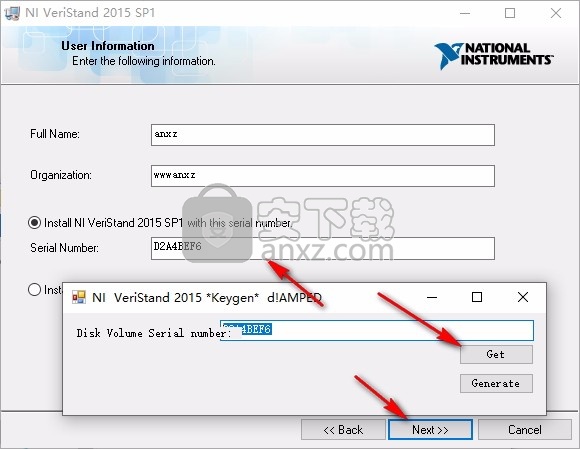

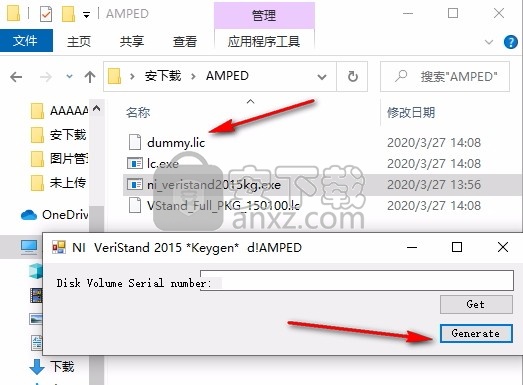

5、然后打开安装包,运行安装包中的注册机(打开安装包“AMPED”运行“ni_veristand2015kg.exe”,),点击Get然后将生成的激活码,将激活码复制到对话框中即可

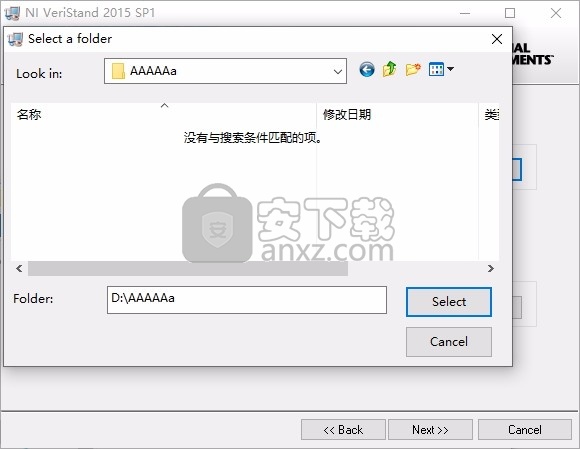

6、可以根据自己的需要点击浏览按钮将应用程序的安装路径进行更改

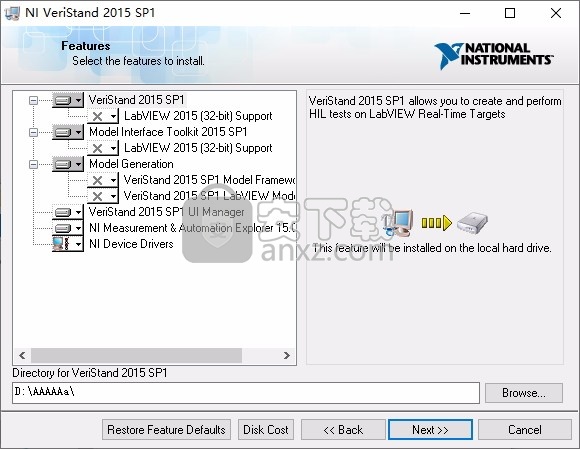

7、弹出以下界面,用户可以直接使用鼠标点击下一步按钮,可以根据您的需要不同的组件进行安装

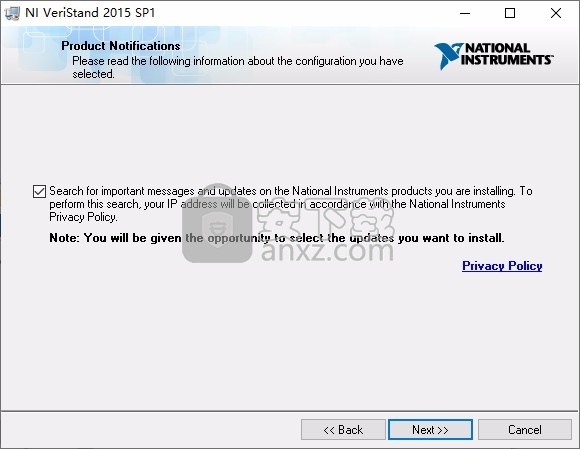

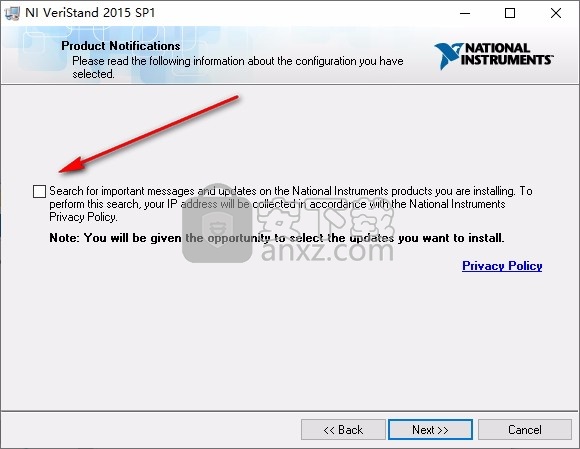

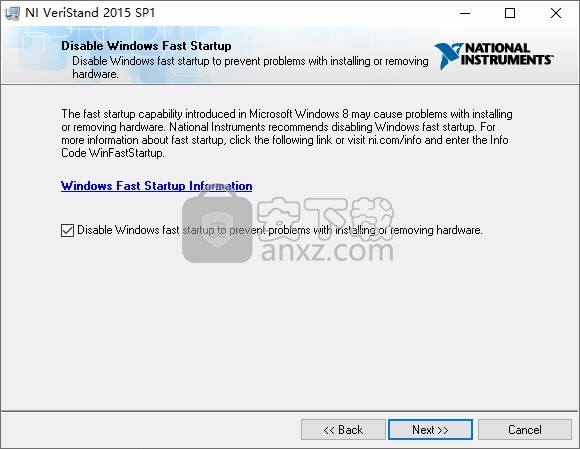

8、产品不更新,去除左下角的勾后点击下一步

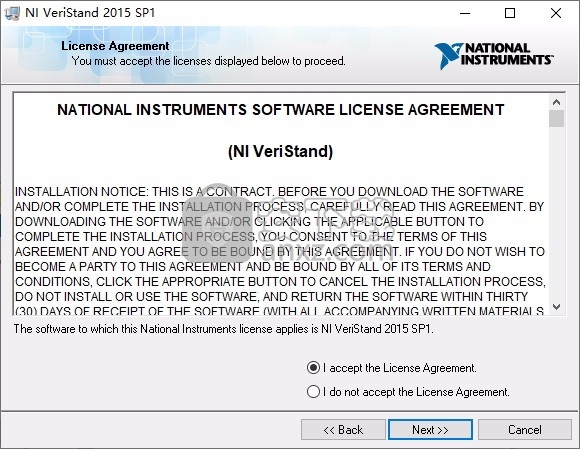

9、同意上述协议条款,然后继续安装应用程序,点击同意按钮即可

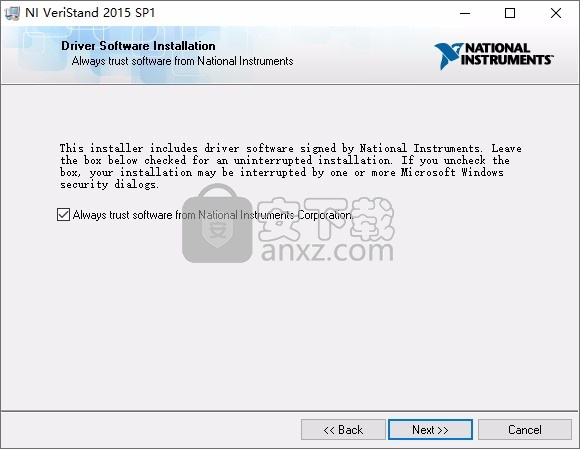

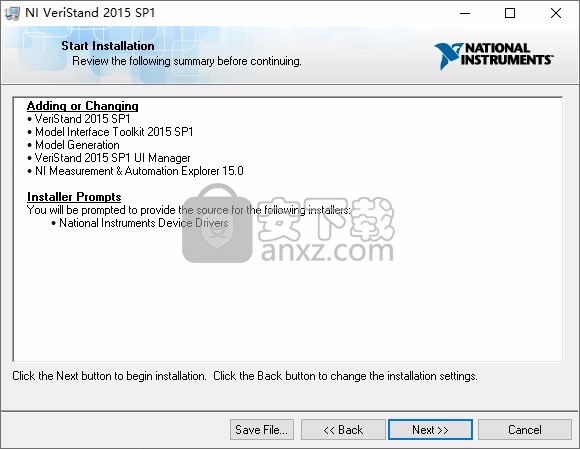

10、现在准备安装主程序,点击安装按钮开始安装

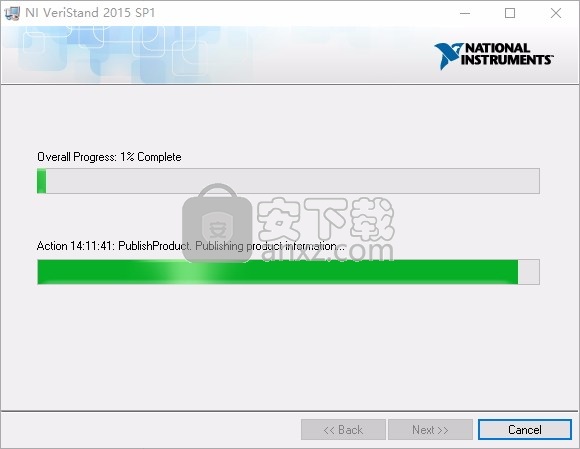

11、弹出应用程序安装进度条加载界面,只需要等待加载完成即可

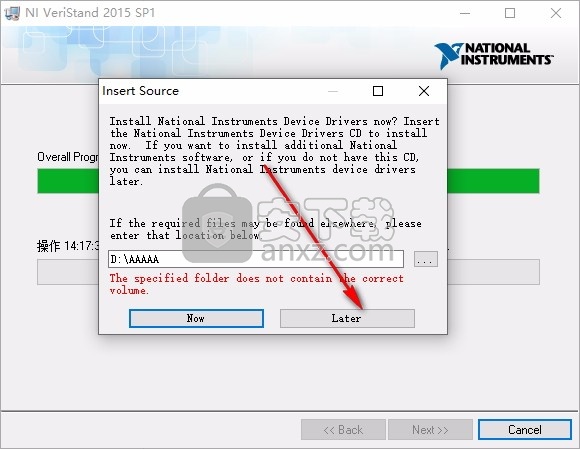

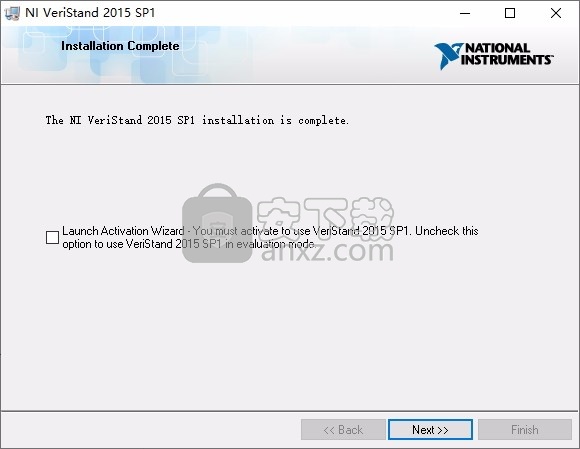

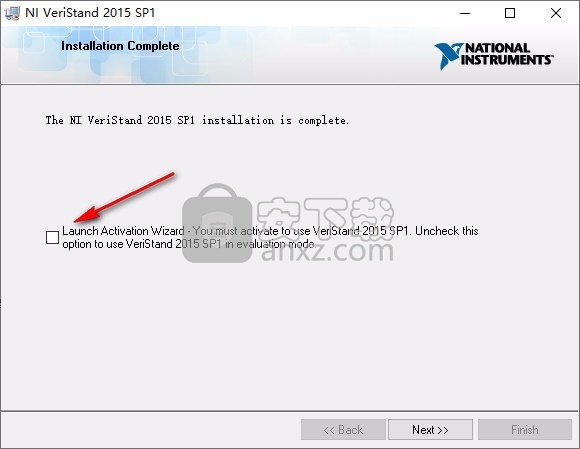

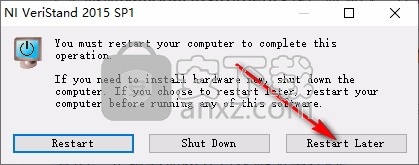

12、根据提示点击安装,弹出程序安装完成界面,点击完成按钮即可

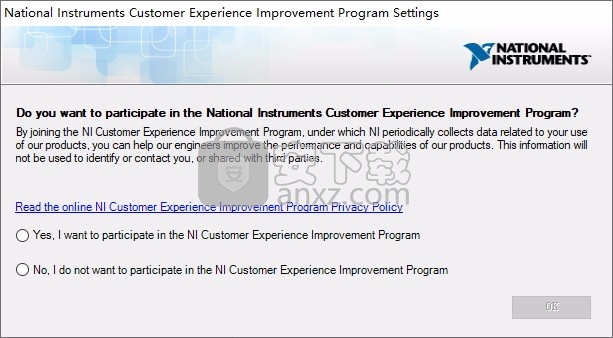

13、根据一系列的设置,有点可以根据自己的需要进行设置

14、如图中标注所示,用户需要根据图中的标注进行操作

15、点击注册机的“Generate”按钮,在当前目录下生成许可证文件“VStand_Full_PKG_150100.lc”

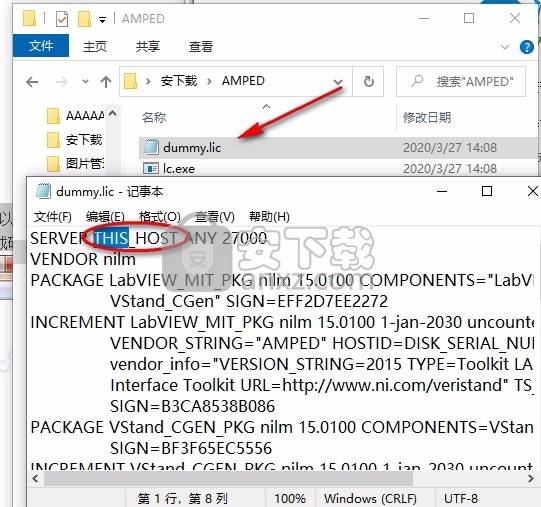

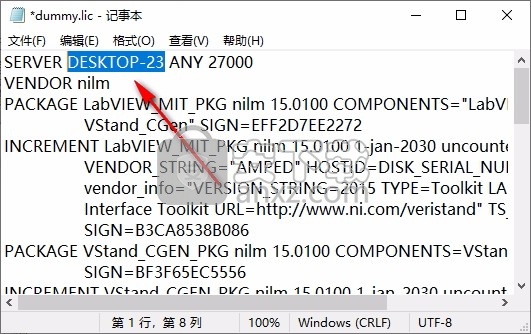

16、以记事本方式打开许可VStand_Full_PKG_150100.lc和dummy.lic,将圈中字符替换为计算机名(右键计算机选择属性可以查看)

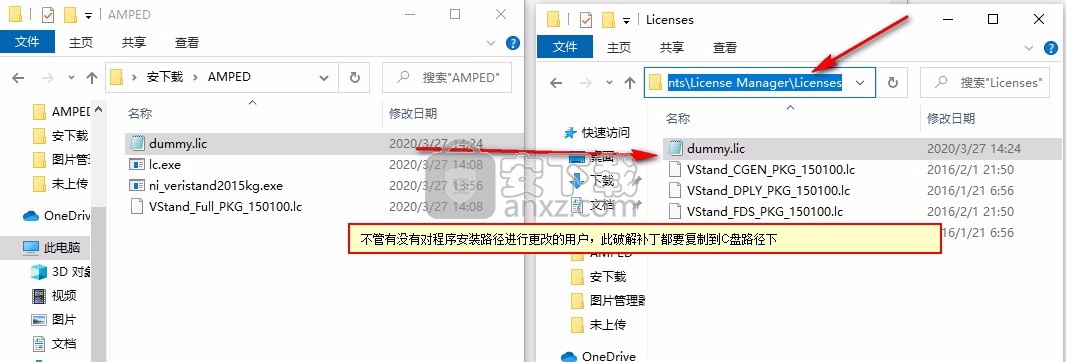

17、然后将其复制到C:\ProgramData\National Instruments\License Manager\Licenses文件夹下即可完成

PS:不管是否更改路径的用户都要复制到C盘中,不在安装路径下

说明

1、完成以上操作步骤后,就可以双击应用程序将其打开,此时您就可以得到对应程序

使用说明

系统资源管理器窗口

在“项目资源管理器”窗口的树中,双击“系统定义文件”节点下的系统定义文件名节点以显示此窗口。您也可以通过选择开始»所有程序»National Instruments»NI VeriStand»System Explorer以独立形式启动“系统资源管理器”窗口。

使用此窗口可以创建和/或修改系统定义文件。您可以通过在系统资源管理器窗口左侧的配置树中添加,删除和修改选项来配置系统定义文件。使用“系统资源管理器”窗口,可以定义系统的各个组件,包括警报,计算出的通道,硬件I / O,系统映射,过程,仿真模型,系统通道,用户通道以及某些VeriStand Engine执行设置。

配置树

窗口左侧的配置树可以包含以下选项,它们对应于特定的配置页面。默认情况下,仅其中一些选项出现。其他(例如某些设备,通道或部分类型)仅在将相关项目添加到系统定义时才会显示。通常,您可以通过单击“添加项目”工具栏按钮或右键单击父项目并选择要添加的子项目来将项目添加到系统定义中。

注意以斜体显示的选项具有用户可配置的名称。它们以默认名称列出在此处。

项目组成

NI VeriStand项目至少包含以下文件,可用于配置,部署和与系统交互:

一个项目文件(.nivsproj)

一个系统定义文件(.nivssdf)

一个屏幕文件(.nivsscr或.nivsscreen)

下图和各节描述了这些文件的角色和位置以及NI VeriStand项目的主要组件。运行项目时,某些组件在系统内部运行。其他组件是您在NI VeriStand环境中创建和配置的用户可见功能。

注意未图示的其他组件将在此插图后的各节中进行介绍。

注意主机和目标计算机可以是同一台台式计算机。在这种情况下,您可以将系统定义文件部署到主机台式PC,就像将文件部署到远程目标一样。

主机

主计算机托管用作操作员用户界面的屏幕文件。该计算机还运行VeriStand网关。主机必须是运行Windows支持版本的PC。

内部特征

VeriStand网关-创建一个TCP / IP通信通道,以促进通过网络与VeriStand Engine的通信。 VeriStand网关从VeriStand引擎接收通道值,并将其存储在表中。您可以使用UI管理器中的“通道数据查看器”选项卡或“通道数据查看器”工作区工具来查看这些值。

如果您在台式机上运行项目,则VeriStand网关会启动VeriStand引擎。如果您在RT目标上运行项目,则VeriStand Gateway会与在RT目标上运行的系统定义文件同步。如果当前在VeriStand Engine上运行的系统定义文件与VeriStand Gateway期望的系统定义文件不匹配,则VeriStand Gateway不会与RT目标上运行的系统定义文件同步。

与您互动的功能

项目文件-定义高级设置的.nivsproj文件,例如:

屏幕和系统定义文件运行

可用用户及其项目权限

您可以从“工作区”窗口的“工具”菜单中启动的工具列表

将项目部署到目标时运行哪些服务

VeriStand网关的IP地址

刺激特征和实时序列

屏幕文件-.nivsscr或.nivs屏幕文件,这些文件定义屏幕的配置和设置,并分别显示您在UI Manager或Workspace窗口中查看的项目。

激励档案-可以调用实时序列,打开和关闭NI VeriStand项目以及执行数据记录和通过/失败分析的测试主管。它还将实时序列连接到系统定义文件,以将系统定义文件中的通道数据绑定到实时序列中的变量。激励配置文件在主机上执行。您可以使用“激励配置文件编辑器”创建并运行激励配置文件。

National Instruments驱动程序软件-您需要适当的National Instruments驱动程序软件来与目标上安装的硬件进行通信。有关所需驱动程序软件的列表,请参见位于 \ National Instruments \ NI VeriStand \ readme \ readme.html的NI VeriStand自述文件。如将NI VeriStand安装在其他位置,请在指定的安装位置找到自述目录。

最高部署目标

NI VeriStand系统中的目标是台式PC或RT目标,可在其上运行系统定义文件和VeriStand Engine。

内部特征

VeriStand Engine-一种不可见的执行机制,用于控制整个系统的时序以及目标与主机之间的通信。 VeriStand Engine由多个定时循环组成,这些循环使用RT FIFO在循环之间传输数据。

注:要将系统定义文件部署到RT目标,必须首先将NI VeriStand的支持文件下载到目标。

与您互动的功能

系统定义文件-您在“系统资源管理器”窗口中配置的.nivssdf文件。系统定义文件包含VeriStand Engine的配置设置,包括:

系统运行的速率。

DAQ设备,NI-XNET设备,FPGA目标或反射存储设备,以及每个设备的任务和通道配置。

要执行的仿真模型及其执行速度。

活动警报列表。您可以使用警报来触发对目标的操作(例如过程),或显示警告用户事件的对话框。

可以在目标上执行的过程的列表。过程是命令脚本,用于定义VeriStand Engine中的一组操作。

系统中数据对象的通道列表。频道类型包括:

硬件I / O通道(DAQ,FPGA等)

模型通道(输入,输出,参数,信号)

用户通道(用于在系统中存储或映射用户定义的值)计算通道(代表系统中其他通道的用户定义计算结果的通道)

确定通道连接方式的系统映射。

模型-实际系统的数学表示。模型通过模拟模拟项目行为的方式产生输出来响应刺激。模型包含与控制系统其他部分通信的输入和输出(称为入口和出口)。

您可以使用几种不同的建模环境来构建模型,然后将模型集成到系统定义文件中。

顶级开发计算机

开发NI VeriStand项目的计算机可能与系统中的主机不同。开发计算机包含NI VeriStand软件。为了扩展NI VeriStand的功能,您还可以在开发计算机上使用以下NI产品:

LabVIEW开发系统—如果要创建自定义设备,工作区控件/指示器,计时设备和/或工具菜单实用程序,则需要LabVIEW开发系统。

LabVIEW Real-Time模块—您需要该模块在自定义设备VI中使用RT函数。

LabVIEW FPGA模块-如果将National Instruments FPGA目标添加到项目,则它必须具有关联的FPGA位文件。 NI VeriStand为某些FPGA设备提供了FPGA位文件。如果要自定义这些FPGA位文件或为另一个FPGA目标创建自定义FPGA位文件,则需要FPGA模块。

了解VeriStand引擎

VeriStand引擎是一种不可见的执行机制,可控制整个系统的时序以及目标计算机与主机计算机之间的通信。 VeriStand Engine由多个定时循环组成,这些循环使用实时(RT)FIFO在循环之间传输数据。每个循环执行某些指定的任务,并具有分配的优先级。尽管您无法更改引擎循环的优先级或主要任务,但是您可以自定义循环的某些操作,例如执行率。系统定义文件包含VeriStand Engine的配置设置。

注意VeriStand Engine通过与VeriStand Gateway进行网络通信来确定要运行哪个系统定义文件。

VeriStand Engine负责执行硬件I / O并运行模型,过程,警报和测试。 VeriStand Engine根据模型执行和硬件I / O的结果计算通道表中的值。该引擎可以在模拟模式的台式PC上运行,也可以在RT系统上作为嵌入式应用程序运行。

下表显示了VeriStand Engine循环的优先级和默认执行率。

VeriStand Engine循环优先级默认执行率

主控制回路H 100 Hz

模型执行环路抽取主控制环路速率

用户定义的异步自定义设备循环H / M / L

波形处理循环L事件驱动

DAQmx波形发生器环路L 10 Hz。也可以由用户定义。

数据处理环路主控制环路速率的抽取

通信发送回路L 15 Hz

通信接收循环L事件驱动

XNET回路L 100 Hz

DIO回路L主控制回路速率的抽取

模型接口循环L事件驱动

下图显示了VeriStand Engine的操作。

主控制回路

主控制循环控制VeriStand Engine的时序,并维护最新的通道值表。对于每次迭代,主控制循环(PCL)执行以下任务:

读写高速FPGA I / O,模拟和计数器DAQ I / O,以及异步自定义设备循环数据。

对数据应用缩放。

如果当前正在运行测试,则执行实时序列的一个步骤。

将数据发送到数据处理循环,以便同步通道值表。

将数据发送到模型执行循环。

提示要执行的数据处理循环,模型执行循环和异步自定义设备循环。

执行软件故障插入。

创建映射连接。

执行嵌入式自定义设备。

从波形处理循环和DAQmx波形产生器循环读取状态信息。

相关链接

PCL执行步骤列表-PCL采取的操作的完整顺序列表。

模型执行循环

每个模型执行循环执行一个相应的已编译模型。模型执行循环数由系统定义文件中指定的模型数决定。对于每次迭代,每个模型执行循环执行以下任务:

读取由主控制循环发送的数据,并将此数据映射到模型入口。

执行模型的一个步骤。

读取模型输出值,并将此数据发送到主控制回路。

请注意,模型执行循环处理与模型输入和输出关联的高速动态数据,而单独的模型接口循环则读取低速异步更新并将其应用于模型参数值。

异步自定义设备循环

您可以确定异步自定义设备循环的数量,行为和优先级。 VeriStand Engine仅负责启动异步自定义设备循环执行,并负责在每次主控制循环迭代时传输自定义设备输入数据值。

波形处理回路

波形处理循环执行以下操作以通过系统传输波形数据:

从DAQmx波形产生器循环读取波形数据。

将波形数据发送到VeriStand网关。

从自定义设备读取波形数据。

将波形数据发送到自定义设备。

DAQmx波形产生器回路

DAQmx波形发生器环路从DAQ设备获取波形。系统定义中的每个波形任务都有一个对应的DAQmx波形产生器循环,该循环执行以下操作:

使用您在任务中定义的定时和触发设置,从DAQ设备上的模拟输入通道读取波形数据。

将波形数据发送到波形处理循环。

如果启用日志记录,则将获取的数据记录到.tdms文件中。

数据处理循环

与主控制循环类似,数据处理循环维护通道值表的完整副本。数据处理循环执行过程,警报和计算通道,并在引擎的各个循环之间分配执行命令

由通信接收循环接收。对于每次迭代,数据处理循环执行以下任务:

从主控制回路接收通道值表。

执行过程,警报和计算出的通道。

将通道值的更新表传输到主控制回路。

将数据值发送到通信发送循环

通讯回路

通信回路保持与VeriStand网关的TCP / IP通信。有两个通信循环:

通信发送循环-将通道值发送到VeriStand网关。

通信接收循环-收听VeriStand网关发送的执行命令。

XNET循环

读取和写入XNET数据。

DIO循环

读取和写入低速数字DAQ I / O数据。

模型接口循环

更新模型参数值。请注意,模型执行循环处理与模型输入和输出关联的高速动态数据,而模型接口循环则读取低速异步更新并将其应用于模型参数值。

PCL执行步骤列表

主控制循环(PCL)通过执行几个执行步骤来控制VeriStand Engine的计时。 PCL可以两种模式之一运行,其中两种模式之间的唯一区别是与模型相关的步骤的时间安排:

在并行模式下,PCL启动模型的执行并继续其下一次迭代,而无需等待模型完成执行。这会在模型开始执行与系统生成模型之间产生一个周期的延迟。

在低延迟模式下,PCL等待模型执行循环完成执行,然后在系统的每次迭代期间读取模型值并将其发布到系统。

相关链接

了解PCL执行和模型延迟

了解VeriStand引擎

并行模式下的PCL执行

PCL在并行模式下采取以下步骤。请注意,步骤4导致模型执行与系统生成数据之间存在一个周期的延迟。

从系统定义中的硬件设备获取输入。注意如果系统包括嵌入式硬件接口定制设备,则在步骤3中执行定制设备的硬件读取数据案例后,PCL会读取DAQ数字线路和计数器。

从上一个迭代读取异步自定义设备FIFO。

在串联硬件接口定制设备的情况下,从硬件运行读取数据。如果配置了硬件缩放比例,NI VeriStand将在获取所有硬件输入后应用缩放比例。

(第二次和后续迭代)从系统定义中的模型读取先前的迭代数据。

从数据处理循环的上一个迭代中读取数据。

处理系统映射。注意VeriStand组件(包括自定义设备)在PCL处理系统映射之前无法读取上一步的数据,即使上一步已获取组件所需的数据也是如此。

运行内联模型接口定制设备的“执行模型”案例。

执行运行实时序列的步骤。注意VeriStand在输入操作之后但在输出操作之前执行实时序列,并继续运行实时序列的每一步,直到序列完成,达到Yield步骤或完成将Auto Yield设置为TRUE的循环迭代为止。如果序列花费的时间比给定的PCL迭代时间长,则PCL会延迟运行。为避免错误,请在整个序列中放置“屈服”步骤并为序列中的任何循环启用“自动屈服”属性,以分步计时。

处理系统映射。

将数据写入数据处理循环。

将数据写入模型。

启动模型的异步执行。

将输出数据写入硬件设备。

运行内联硬件接口定制设备的写入数据到硬件案例。

将数据写入异步自定义设备FIFO。

低延迟模式下的TopPCL执行

PCL在低延迟模式下采取以下步骤,因为它在模型之间传输数据。请注意,PCL在继续执行模型之前等待模型完成执行(步骤9)。当模型完成执行时,PCL在模型生成数据的同一迭代期间将数据从模型提供给其他循环。

注意National Instruments建议仅在需要最小化输入,模型执行和输出之间的延迟时才选择此模式。在每次迭代中等待模型执行循环读取,执行和写入操作会大大降低系统的执行速度。

从系统定义中的硬件设备获取输入。注意如果系统包括嵌入式硬件接口定制设备,则在步骤3中执行定制设备的硬件读取数据案例后,PCL会读取DAQ数字线路和计数器。

从上一个迭代读取异步自定义设备FIFO。

在串联硬件接口定制设备的情况下,从硬件运行读取数据。如果您配置了硬件缩放,则VeriStand在获取所有硬件输入后将应用缩放。

从数据处理循环的上一个迭代中读取数据。

处理系统映射。注意VeriStand组件(包括自定义设备)在PCL处理系统映射之前无法读取上一步的数据,即使上一步已获取组件所需的数据也是如此。

运行内联模型接口定制设备的“执行模型”案例。

执行运行实时序列的步骤。注意VeriStand在输入操作之后但在输出操作之前执行实时序列,并继续运行实时序列的每一步,直到序列完成,达到Yield步骤或完成将Auto Yield设置为TRUE的循环迭代为止。如果序列花费的时间比给定的PCL迭代时间长,则PCL会延迟运行。为避免错误,请在整个序列中放置“屈服”步骤,并启用“自动屈服”属性

序列中的任何循环。

处理系统映射。

将数据写入模型。

启动模型的执行,并等待它们完成执行。

从模型读取数据。

处理系统映射。

将数据写入数据处理循环。

将输出数据写入硬件设备。

运行内联硬件接口定制设备的写入数据到硬件案例。

将数据写入异步自定义设备FIFO。

相关链接

内联硬件接口自定义设备

创建一个新项目或打开一个现有项目

NI VeriStand项目至少由一个项目文件(.nivsproj),一个系统定义文件(.nivssdf)和一个屏幕文件(.nivsscreen)组成。项目还可以包含受支持的NI硬件,自定义设备,编译的模型,使用The MathWorks,Inc.Simulink®软件环境开发的模型,任何自定义VI等。

完成以下步骤以创建新的项目文件和系统定义文件。

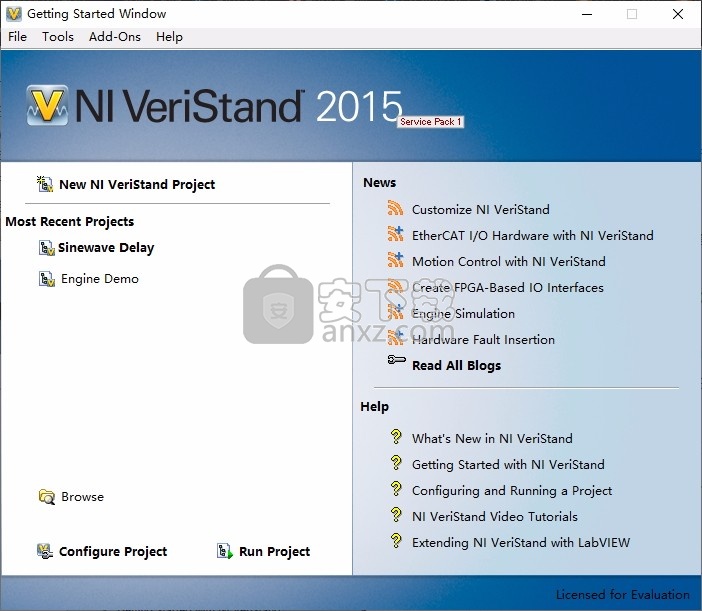

启动NI VeriStand以显示“入门”窗口。

在“入门”窗口中,选择“新建NI VeriStand项目”以显示“创建新项目”对话框。

在“项目名称”文本框中输入项目名称。

创建新项目时,NI VeriStand自动创建一个新的系统定义文件,并将系统定义文件命名为与项目文件相同的名称。您也可以通过从“创建新项目”对话框的“系统定义”页面上的“使用项目名称”复选框中删除选中标记来手动输入其他文件名。

要使用现有的系统定义文件,请完成以下步骤。

单击系统定义选项卡,并启用使用现有的NI VeriStand系统定义文件单选按钮,以显示选择系统定义文件对话框。

导航到要使用的系统定义文件。

单击确定按钮。

完成以下步骤,打开先前配置的NI VeriStand项目。

启动NI VeriStand以显示“入门”窗口。

从“最新项目”列表中选择一个现有项目。

单击“配置项目”以在“项目资源管理器”窗口中打开项目。

通过在“系统资源管理器”窗口中选择“文件”»“新建”,您也可以创建新的系统定义文件而无需创建新项目。

人气软件

-

南方cass 65.9 MB

/简体中文 -

迈迪工具集 211.0 MB

/简体中文 -

origin(函数绘图工具) 88.0 MB

/简体中文 -

OriginLab OriginPro2018中文 493.0 MB

/简体中文 -

探索者TssD2017 417.0 MB

/简体中文 -

mapgis10.3中文(数据收集与管理工具) 168.66 MB

/简体中文 -

刻绘大师绿色版 8.32 MB

/简体中文 -

SigmaPlot 119 MB

/简体中文 -

keyshot6 1024 MB

/简体中文 -

Matlab 2016b 8376 MB

/简体中文

女娲设计器(GEditor) v3.0.0.1 绿色版

女娲设计器(GEditor) v3.0.0.1 绿色版  iMindQ(思维导图软件) v8.1.2 中文

iMindQ(思维导图软件) v8.1.2 中文  Altair Embed(嵌入式系统开发工具) v2019.01 附带安装教程

Altair Embed(嵌入式系统开发工具) v2019.01 附带安装教程  avizo 2019.1(avizo三维可视化软件) 附安装教程

avizo 2019.1(avizo三维可视化软件) 附安装教程  ChemOffice 2017 附带安装教程

ChemOffice 2017 附带安装教程  绘图助手 v1.0

绘图助手 v1.0