Mentor Graphics QuestaSim 2021.1文件

附安装教程- 软件大小:2.43 MB

- 更新日期:2021-03-29 12:06

- 软件语言:英文

- 软件类别:驱动补丁

- 软件授权:修改版

- 软件官网:待审核

- 适用平台:WinXP, Win7, Win8, Win10, WinAll

- 软件厂商:

软件介绍 人气软件 下载地址

QuestaSim2021是一款功能丰富的电气仿真软件,如果你需要在电脑上仿真设计电气设备就可以下载这款软件,该软件拥有先进的模拟技术,可以在软件执行多种模拟项目,可以在软件配置硬件,可以添加电气组件,可以运行测试仿真流程,可以生成报告内容,可以使用Questa验证IP库组件验证设计,可以使用数据集记录模拟结果,使用断言和Cover指令进行验证,使用数据流窗口进行调试,提供的仿真和分析功能非常多,满足大部分仿真工程需求,这里小编推荐的是QuestaSim2021补丁,使用补丁将软件激活就可以免费使用该软件创建仿真项目!

软件功能

一、使用vopt优化设计

默认情况下,Questa SIM对您的设计执行内置优化,以最大化模拟器性能。

这些优化限制了设计对象的可见性,但是您可以出于调试目的而提高任何对象的可见性,请参阅“保留对象的可见性以进行调试”。

在Questa SIM中用于执行全局优化的命令是vopt。本章讨论vopt功能,优化对设计的影响以及如何自定义vopt在设计中的应用。

二、项目资源

项目是规范或测试下设计的文件和用户定义的设置的集合。至少,一个项目具有一个根目录,一个工作库和“元数据”,它们存储在位于项目根目录下的.mpf文件中。元数据包括:编译器开关设置,编译顺序和文件映射。

项目可能还包括以下项目:

源文件或对源文件的引用

其他文件,例如自述文件或其他项目文档

本地图书馆

引用全球图书馆

模拟配置

资料夹

三、设计库

VHDL设计与库相关联,库是包含已编译设计单元的对象。 Questa SIM中模拟的SystemC,Verilog和SystemVerilog设计也被编译到库中。

四、VHDL模拟

Questa SIM使您能够编译,优化,加载和仿真VHDL设计。

五、波形分析

Wave窗口是在仿真后用于分析和调试设计的最常用工具。 它以波形和信号值的形式显示设计中的所有信号,并提供一套用于调试的图形工具。

六、约束随机刺激的验证

SystemVerilog支持具有随机约束的自动测试平台开发,使您能够自动生成用于功能验证的测试平台。 SystemVerilog提供了一种面向对象的方法,用于指定对随机测试基准值的约束。 然后,Questa SIM使用约束求解器处理这些约束,该求解器生成满足这些约束的随机值。 约束求解器性能分析使您可以查看花费了多少时间来约束哪些约束,以及哪些是最昂贵的约束。 它还可以分析在求解器“区域”中花费的CPU时间,而不是每个函数调用所花费的时间。

七、有限状态机

有限状态机(FSM)反映了从仿真开始到现在的基于状态的设计所经历的变化。 转换指示状态更改,并通过启用它们所需的条件来描述。 由于FSM的复杂性,包含它们的设计可能包含大量缺陷。 因此,在进入设计周期的下一步综合之前,分析RTL中的FSM非常重要。

安装方法

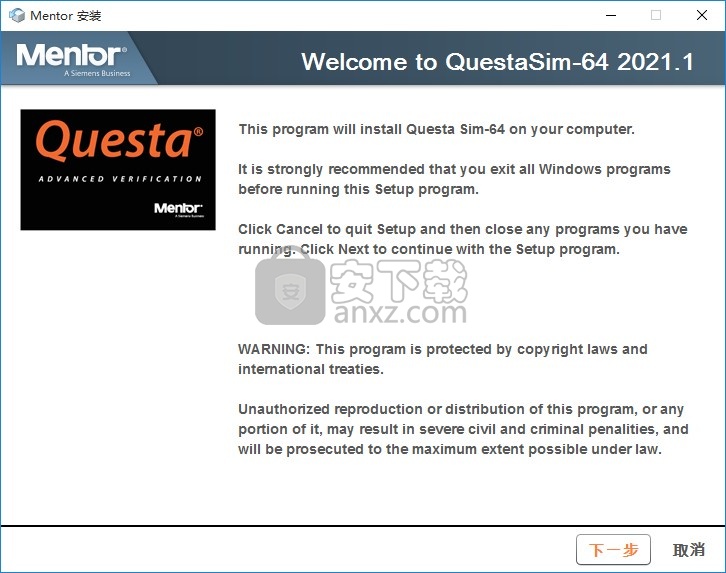

1、打开questasim-win64-2021.1.exe开始安装软件

2、提示软件的安装地址设置C:\questasim64_2021.1

3、小编将软件安装到E盘

4、阅读软件的协议内容,点击同意

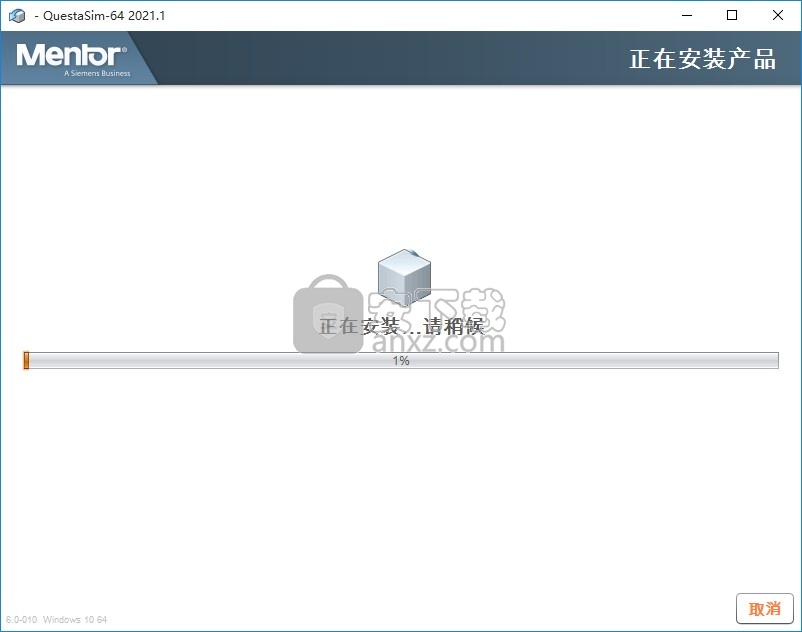

5、提示软件的安装过程,等待安装结束

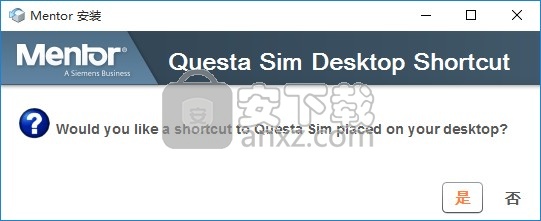

6、提示是否创建桌面启动图标,可以点击是

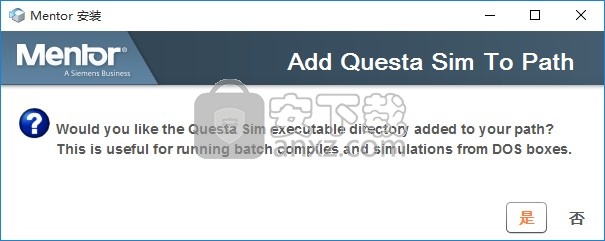

7、提示您想将Questa Sim可执行目录添加到您的路径吗?

这对于从DOS盒运行批处理编译和模拟非常有用,可以点击是

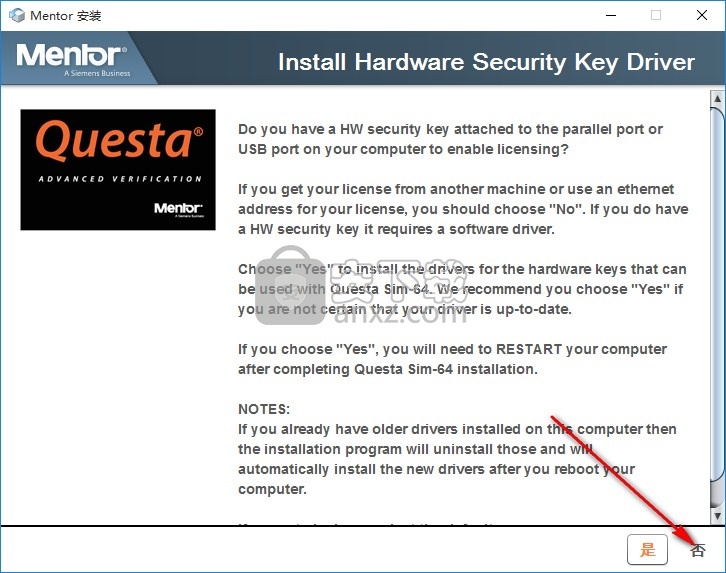

8、提示安装结束,点击否

9、到这里软件就安装完毕了,点击完成

方法

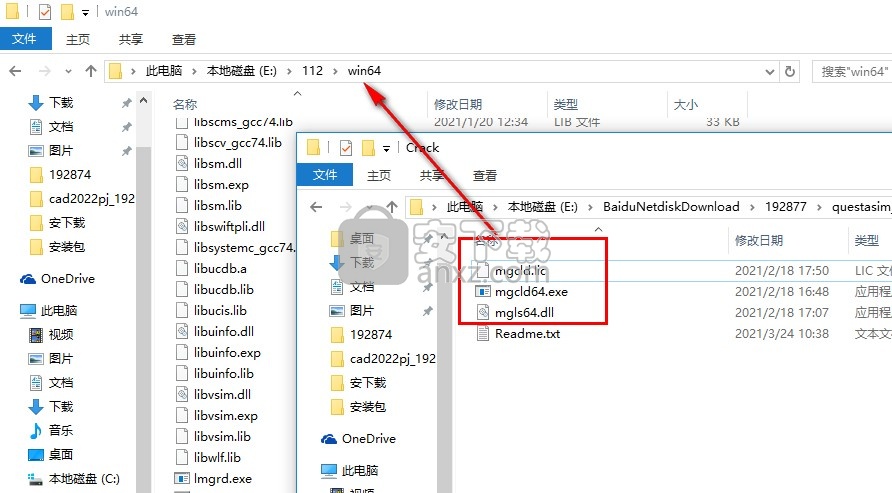

1、将三个补丁复制到软件安装地址下的win64文件夹中替换同名文件

2、选择此电脑-属性-高级设置建立系统环境-创建系统变量

3、变量名称:LM_LICENSE_FILE,变量值E:\112\win64\mgcld.lic(许可证地址),点击确定

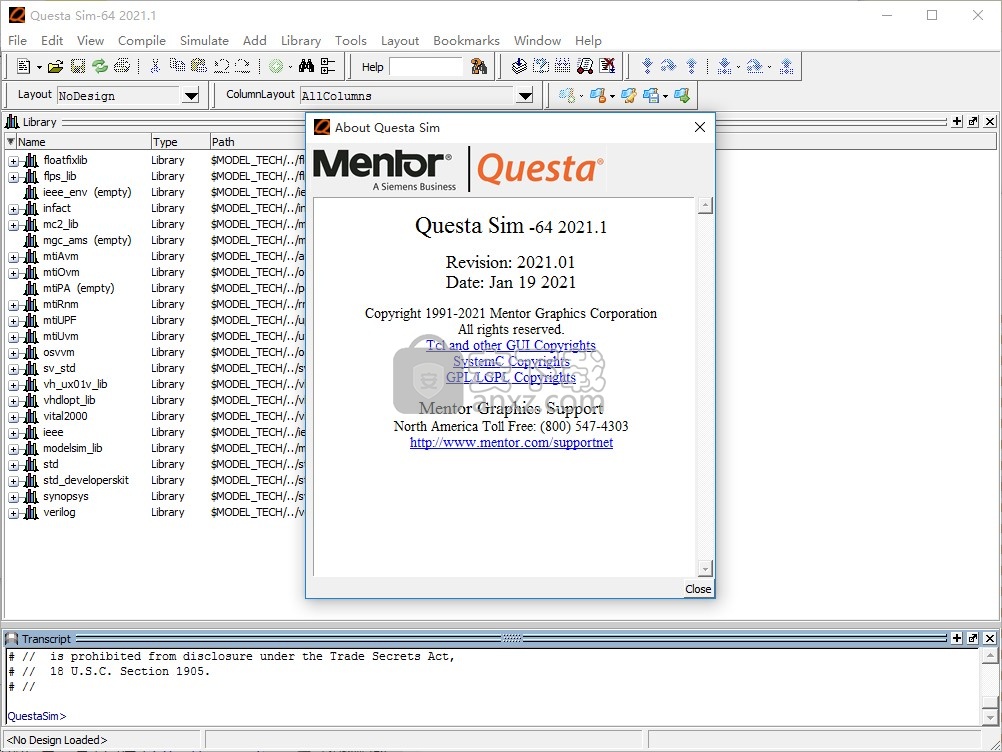

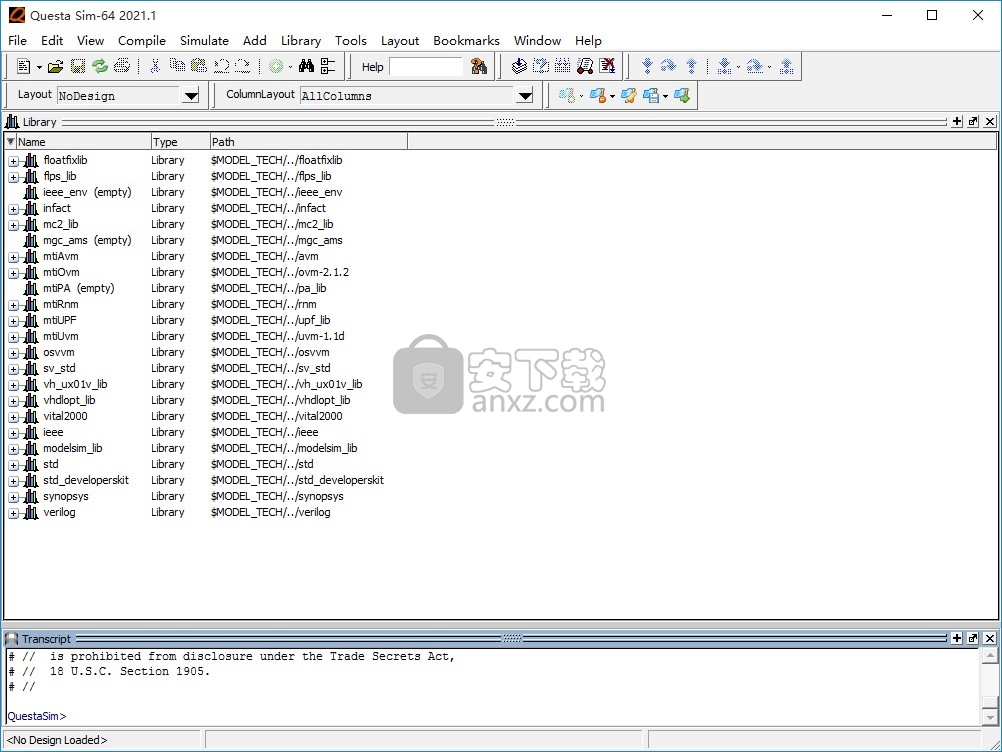

4、打开软件就可以正常使用,这里是软件的启动界面

5、正常进入软件说明激活成功,现在QuestaSim完毕

使用说明

FSM识别

Questa SIM可以识别VHDL和Verilog FSM。

当您在GUI中收集FSM覆盖率度量标准或查看FSM信息以及它们符合以下条件时,将在编译或优化过程中识别FSM:

状态变量可以容纳的状态数量有限。

对状态变量的下一个状态分配是在一个时钟下进行的。

下一个状态值取决于状态变量的当前状态值。

不依赖于当前状态值的状态分配被视为重置分配。

Questa SIM可以识别以下VHDL和Verilog FSM设计样式:

使用当前状态变量的FSM。

使用当前状态和下一状态变量的FSM。

FSM使用多个下一个状态变量,其中所有这些都用作缓冲区分配。

使用固定的非浮动参数/泛型的FSM(仅在使用vopt时受支持)。

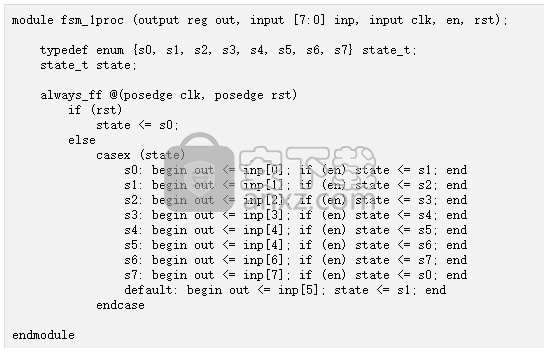

使用单个或多个Case语句的FSM。

使用单个或多个If-Else语句的FSM。

使用混合If-Else和Case语句的FSM。

使用VHDL等待/选择语句的FSM。

FSM仅将VHDL when / else语句用于并发分配。

FSM通过AND或OR运算符使用复杂的“ if”条件。

使用一热或一冷样式定义的FSM(仅支持Verilog)。

FSM使用可以静态评估为常量的下一状态分配。

FSM使用当前或下一个状态变量作为VHDL记录或SystemVerilog结构字段。不支持嵌套结构。

FSM使用当前或下一个状态变量作为VHDL或Verilog索引表达式。

FSM完全在Verilog任务中定义。

使用任何集成SystemVerilog类型的FSM,例如逻辑,整数,bit_vector,枚举,打包结构。还支持这些类型的Typedef。

FSM在VHDL中使用多字段记录类型,其中状态变量是记录的字段,完整记录用于在计时过程中驱动当前状态。

Verilog FSM具有分配给'x(未知)值的状态变量。默认情况下,X分配处于启用状态。

不支持的FSM设计样式

Questa SIM无法识别以下设计样式:

使用Verilog局部选择表达式作为当前状态变量。

使用VHDL切片表达式作为当前状态变量。

在多个模块中定义单个FSM。

对当前/下一个状态变量使用混合的阻塞和非阻塞分配。

FSM设计风格示例

以下示例说明了几种受支持的FSM设计样式。

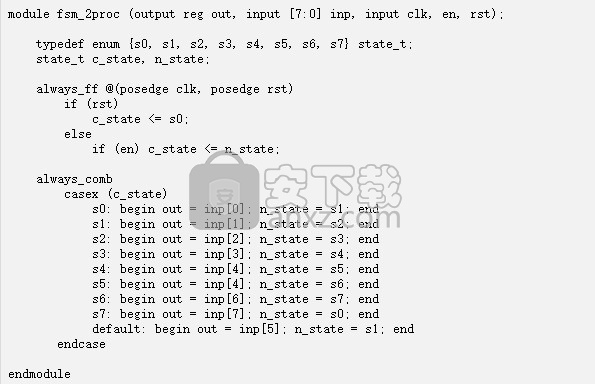

示例1. Verilog单状态变量FSM

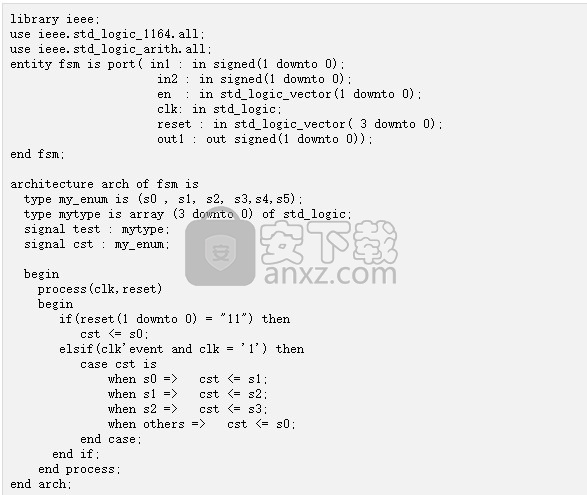

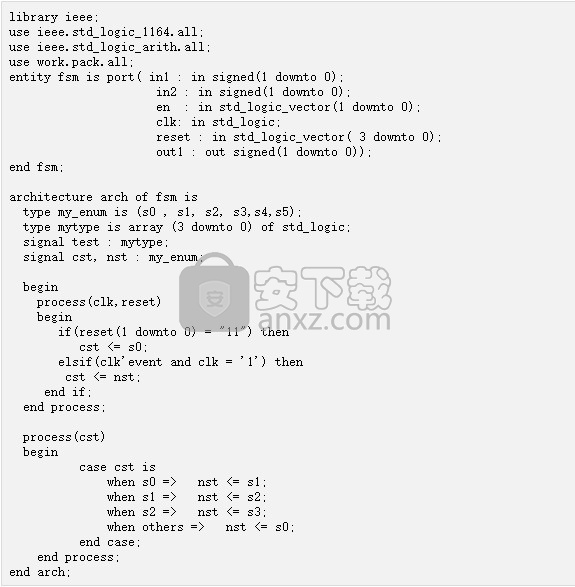

例子2. VHDL单状态变量FSM

示例3.具有单个下一个状态变量FSM的Verilog当前状态变量

例子4. VHDL当前状态变量和单个下一个状态变量FSM

FSM覆盖率

Questa SIM在仿真之前的编译阶段识别您设计中的FSM。模拟阶段收集有关在使用DUT模拟测试平台时使用了哪些状态和转换的覆盖率度量。

为FSM收集了以下指标:

State Coverage Metric(状态覆盖率指标)—确定在仿真过程中已达到多少个FSM状态。

Transition Coverage Metric(过渡覆盖率指标)—确定在状态机模拟中执行了多少次过渡。

多状态过渡覆盖范围(或序列覆盖范围)-跟踪状态机模拟中已执行的各种可能的过渡序列。

FSM多状态转换

多状态转换也称为状态序列。

在覆盖域中,将-fsmmultitrans开关与vcom或vlog或vopt一起使用会产生一个有时称为序列覆盖的度量,因为它通过状态序列测量FSM的进度。 FSM识别消息将多状态转换显示为:

#S0 => S1 => S0

指定-fsmmultitrans时,可以在以下位置查看此信息:

成绩单中的FSM识别信息注释,特别是多状态转换表。

FSM覆盖文本报告,特别是覆盖的过渡表和未覆盖的过渡表。

详细信息窗口。

FSM的“代码覆盖率分析”窗口。

报告FSM的覆盖率指标

您可以使用GUI或coverage报告命令来为设计中的FSM创建coverage度量的文本报告。

先决条件

运行模拟以收集FSM的覆盖范围指标。

(可选)从coverage集合中排除过渡或状态。这使您可以达到100%FSM覆盖率。有关更多信息,请参阅“ FSM承保范围”部分。

程序

1、选择工具>覆盖率报告>文本。

显示“覆盖文本报告”对话框。

2、从“报告于”下拉菜单中,选择以下选项之一:

所有文件-报告每个文件中定义的所有设计单位的FSM数据。 (带覆盖率报告的按文件切换)

所有实例-报告每个实例中所有FSM的数据,并合并在一起。 (根据覆盖率报告)

所有设计单元-报告每个设计单元所有实例中所有FSM的数据,并合并在一起。 (-bydu带有覆盖率报告)

3、在“覆盖类型”窗格中,确保选择了Fsms。 (代码为f的覆盖率报告)

4、根据需要更改其他任何选项。

5、点击确定

结果

将报告(report.txt)写入当前工作目录。

打开一个包含report.txt文件的记事本窗口。

使用位置图引用源文件

引用库中源文件的Questa SIM工具以两种方式查找源文件。

如果存储在库中的路径名完整,则这是用于引用文件的路径。

如果路径名是相对的,则该工具将查找相对于当前工作目录的文件。 如果此文件不存在,则使用相对于库中存储的工作目录的路径。

如果库是在单个系统上创建和使用的,则这种引用源文件的方法通常可以正常工作。 但是,当多个系统通过网络访问库时,物理路径名并不总是相同的,并且源文件引用规则也不总是有效。

使用位置映射

位置图用于将库中物理路径名的前缀替换为环境变量。 位置图定义了物理路径名前缀和环境变量之间的映射。

如果设置了MGC_LOCATION_MAP环境变量,则Questa SIM卡工具将在调用时打开位置图文件。 如果未设置MGC_LOCATION_MAP,则Questa SIM将在以下位置按顺序查找名为mgc_location_map的文件:

当前目录

您的主目录

包含Questa SIM二进制文件的目录

Questa SIM安装目录

您可以分两步映射文件。

程序

1、将环境变量MGC_LOCATION_MAP设置为位置地图文件的路径。

2、指定从物理路径名到逻辑路径名的映射:

路径名语法

逻辑路径名必须以$开头,而物理路径名必须以/开头。逻辑路径名后跟一个或多个等效的物理路径名。如果物理路径名引用相同的物理目录,则它们是等效的(它们在不同的系统上只是具有不同的路径名)。

位置映射的工作原理

存储路径名时,会尝试将物理路径名映射到相对于逻辑路径名的路径。

这是通过在位置图文件中搜索第一个物理路径名来完成的,该路径名是所讨论路径名的前缀。然后,将逻辑路径名替换为前缀。例如,“ / usr / vhdl / src / test.vhd”映射到“ $ SRC / test.vhd”。如果可以映射到逻辑路径名,则这是保存的路径名。库中设计单元的源文件条目的路径是典型映射的一个很好的示例。

为了从逻辑路径名映射回物理路径名,Questa SIM期望为每个逻辑路径名(具有相同的名称)设置一个环境变量。调用工具时,Questa SIM会读取位置地图文件。如果您的外壳中尚未设置与逻辑路径名相对应的环境变量,那么Questa SIM会将变量设置为位置映射中逻辑路径名之后的第一个物理路径名。例如,如果您未设置SRC环境变量,则Questa SIM会自动将其设置为“ / home / vhdl / src”。

留言系统

Questa SIM消息系统可帮助您在使用应用程序时识别问题并进行故障排除。消息在“成绩单”窗口中以标准格式显示。

因此,您还可以从保存的成绩单文件访问它们(有关更多详细信息,请参阅保存成绩单文件)。

比较分层设计和展平设计

如果将分层的RTL设计仿真与展平的综合设计仿真进行比较,则可能具有不同的层次结构,不同的信号名称,并且在门级设计中总线可能会分解为一位信号。所有这些差异都可以通过Questa SIM的波形比较功能来解决。

如果测试设计是分层的,但是其层次结构与参考设计的层次结构不同,则可以使用compare add命令指定测试设计中的哪个区域路径与参考设计中的区域路径相对应。

如果测试设计是平坦的,并且测试信号名称与参考信号名称不同,则compare add命令允许您指定将测试设计中的哪个信号与参考设计中的哪个信号进行比较。

此外,如果总线已经拆除或“爆破”,则可以使用compare add命令的-rebuild选项在测试设计中自动重建总线。这样一来,您就可以将一辆公共汽车与另一辆公共汽车区别对待。

如果RTL测试设计中的信号类型与参考设计中的合成信号类型不同(例如,寄存器与网络),则“波形比较”功能将自动为您进行类型转换。如果类型差异过大(例如整数与实数),则Waveform Compare会通知您。

保存和重新加载比较结果

要保存比较结果以备将来使用,必须同时保存比较设置规则和比较差异。

程序

要保存规则,请选择“工具”>“波形比较”>“规则”>“保存”。 该文件将包含用于复制比较的所有规则。 默认文件名为“ compare.rul”。

要保存差异,请选择工具>波形比较>差异>保存。 默认文件名为“ compare.dif”。

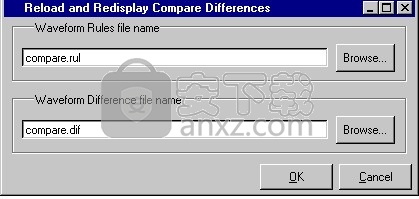

要在以后重新加载比较结果,请选择“工具”>“波形比较”>“重新加载”,然后指定规则和差异文件。

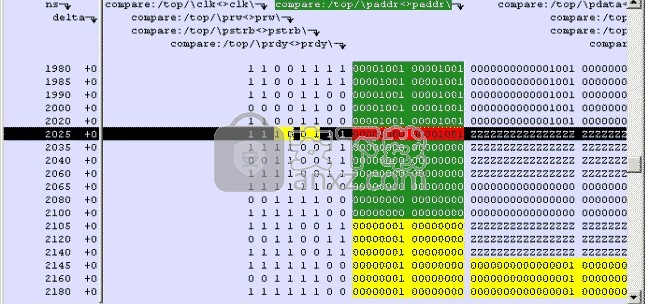

图1.重新加载并重新显示比较差异

查看文本格式的差异

您还可以在“主”窗口的“成绩单”窗格中或在已保存的文件中查看差异的文本输出。

程序

1、要查看记录中的差异,请选择工具>波形比较>差异>显示。

2、要将差异保存到文本文件中,请选择“工具”>“波形比较”>“差异”>“写报告”。

在列表窗口中查看差异

比较对象也可以显示在“列表”窗口中。 差异以黄色背景突出显示。 在选定列上进行制表可将选择内容移至下一个差异(实际上是差异边缘)。 Shift-Tab键将选择向后移动。

图1.列表窗口中的波形差异

右键单击以黄色突出显示的差异,将为您提供三个选项:“差异信息”,“注释差异”和“忽略/忽略差异”。 使用这些选项,您可以选择显示差异信息,可以忽略选定的差异或关闭忽略,并且可以注释单个差异

人气软件

-

NVIDIA Control Panel(NVIDIA控制面板) 8.25 MB

/简体中文 -

microsoft visual c++ 2019(vc2019运行库) 28.3 MB

/简体中文 -

.NET Framework 3.5 cab格式离线安装包 68.6 MB

/简体中文 -

originpro2020激活码 0 MB

/简体中文 -

autocad2022注册机 0.1 MB

/简体中文 -

浩辰CAD2021中文专业版补丁 1.33 MB

/简体中文 -

xmind112021补丁 55.0 MB

/简体中文 -

Aisino SK-820票据打印机驱动 0.54 MB

/简体中文 -

福昕高级PDF编辑器10.0企业版补丁 41.7 MB

/简体中文 -

securefx9.0文件 4.68 MB

/英文

驱动精灵万能网卡版电脑版 2021.12.15.104

驱动精灵万能网卡版电脑版 2021.12.15.104  Siemens Simcenter Flotherm XT 2020.2文件 附激活教程

Siemens Simcenter Flotherm XT 2020.2文件 附激活教程  Autodesk Fabrication ESTmep 2022文件 附激活教程

Autodesk Fabrication ESTmep 2022文件 附激活教程  Geomagic Control X2020注册机 附安装教程

Geomagic Control X2020注册机 附安装教程  jetbrains datagrip 2021.1文件 含激活和汉化教程

jetbrains datagrip 2021.1文件 含激活和汉化教程